在英特爾IFS Direct Connect活動日前夕�,公司通過分享其未來數(shù)據(jù)中心處理器的一瞥�����,概述了它將為其代工客戶提供的新芯片技術(shù)�����。這些進(jìn)步包括通過3D堆疊,實現(xiàn)了更密集的邏輯以及連接性增加16倍�,它們將是該公司與其他公司的芯片架構(gòu)師共享的首批高端技術(shù)之一。

這些新技術(shù)將達(dá)到英特爾長達(dá)數(shù)年轉(zhuǎn)型的頂峰�����,這家處理器制造商正在從一家只生產(chǎn)自己芯片的公司轉(zhuǎn)變?yōu)橐患掖S����,為其他公司生產(chǎn)芯片���,并將自己的產(chǎn)品團(tuán)隊視為另一個客戶,圣何塞的IFS Direct Connect活動旨在作為新商業(yè)模式的亮相派對�����。

在內(nèi)部���,英特爾計劃在代號為Clearwater Forest的服務(wù)器CPU中使用這些技術(shù)的組合����。該公司認(rèn)為該產(chǎn)品是一種具有數(shù)千億個晶體管的片上系統(tǒng)����,是其為其他客戶提供代工服務(wù)的一個目標(biāo)或案例。

英特爾數(shù)據(jù)中心技術(shù)總監(jiān)Eric Fetzer表示���,“我們的目標(biāo)是讓計算達(dá)到最佳每瓦性能”�。這意味著使用該公司最先進(jìn)的制造技術(shù)Intel 18A����?���!?/p>

“但是�,如果我們將該技術(shù)應(yīng)用于整個系統(tǒng),就會遇到其他潛在問題�,”他補(bǔ)充道?��!跋到y(tǒng)的某些部分不一定能像其他部分一樣擴(kuò)展�。邏輯通?���?梢愿鶕?jù)摩爾定律很好地擴(kuò)展一代又一代?�!钡渌δ軇t不然����。例如��,SRAM(CPU的高速緩存)一直滯后于邏輯�。連接處理器和計算機(jī)其余部分的I/O電路則更加落后。

面對這些現(xiàn)實���,英特爾將Clearwater Forest的系統(tǒng)分解為其核心功能����,選擇最適合的技術(shù)來構(gòu)建每個功能,并使用一套新技術(shù)將它們重新縫合在一起�。其結(jié)果是CPU能夠擴(kuò)展到多達(dá)3000億個晶體管。

在Clearwater Forest�����,數(shù)十億記個晶體管被分為三種不同類型的硅IC�,即芯片或小芯片,它們互連并封裝在一起�����。該系統(tǒng)的核心是使用Intel 18A工藝構(gòu)建的多達(dá)12個處理器核心小芯片��。這些小芯片以3D方式堆疊在三個使用Intel 3構(gòu)建的“基礎(chǔ)芯片”之上��,該工藝為今年推出的Sierra Forest CPU制造計算核心�����。CPU的主高速緩存、電壓調(diào)節(jié)器和內(nèi)部網(wǎng)絡(luò)將安裝在基礎(chǔ)芯片上�。“堆疊通過縮短路徑來改善計算和內(nèi)存之間的延遲��,同時啟用更大的緩存����。”高級首席工程師Pushkar Ranade說道����。

最后,CPU的I/O系統(tǒng)將位于使用Intel 7構(gòu)建的兩個芯片上�����,這些小芯片與Sierra Forest和Granite Rapids CPU中的小芯片基本相同���,從而減少了開發(fā)費(fèi)用�。

以下是所涉及的新技術(shù)及其提供的功能:

首先是3D混合鍵合技術(shù)�����。英特爾當(dāng)前的芯片堆疊互連技術(shù)Foveros將一個芯片連接到另一個芯片�����,使芯片封裝的尺寸大幅縮小����,通過焊料的微小“微凸塊”短暫熔化以連接芯片。這使得Meteor Lake CPU中使用的Foveros版本大約每36微米建立一個連接���。而Clearwater Forest將使用新技術(shù)Foveros Direct 3D�����,該技術(shù)不同于基于焊接的方法�����,可將3D連接的密度提高16倍��。它被稱為“混合鍵合”��,類似于將兩個芯片表面的銅焊盤焊接在一起��。這些墊片稍微凹陷并被絕緣體包圍�。當(dāng)將兩個芯片壓在一起時�����,一個芯片上的絕緣體會粘附到另一芯片上。然后��,對堆疊的芯片進(jìn)行加熱��,使銅在間隙中膨脹并粘合在一起���,形成永久鏈接�����。

Fetzer表示��,“混合鍵合互連能夠大幅提高連接密度���。這種密度對于服務(wù)器市場非常重要,特別是因為這種密度可以實現(xiàn)更低的連接功耗�����?�!比绻勘忍氐哪茉闯杀咎?,數(shù)據(jù)從一個硅芯片傳輸?shù)搅硪粋€硅芯片所涉及的能量很容易消耗產(chǎn)品功率預(yù)算的一大部分�����。而Foveros Direct 3D使每比特的功耗成本降至0.05皮焦耳以下,這使其與在硅芯片內(nèi)搬運(yùn)數(shù)據(jù)所需的能量處于同一規(guī)模�。

節(jié)省的大部分能源來自于傳輸更少銅線的數(shù)據(jù)。假設(shè)想要將一個芯片上的512線總線連接到另一個芯片上���,以便兩個芯片可以共享一組一致的信息��。在每個芯片上��,這些總線可能窄至每微米10-20根總線�����。而使用當(dāng)今的36微米間距微凸塊技術(shù)將信號從一個芯片傳輸?shù)搅硪粋€芯片���,意味著將這些信號分散到一側(cè)數(shù)百平方微米的硅上,然后將它們聚集到另一側(cè)的同一區(qū)域�����。所有額外的銅和焊料“會給延遲和功率帶來問題”�。相比之下����,混合鍵合可以在幾個微凸塊占據(jù)的同一區(qū)域中進(jìn)行總線到總線的連接�����。

盡管這些好處可能很大��,但轉(zhuǎn)向混合鍵合并不容易���。要形成混合鍵合���,需要將已經(jīng)切割的硅芯片與仍附著在晶圓上的硅芯片連接起來。正確對齊所有連接意味著芯片必須被切割成比微凸塊技術(shù)所需的公差大得多的公差����。修復(fù)和恢復(fù)也需要不同的技術(shù)。Fetzer表示�,甚至連接失敗的主要方式也是不同的。對于微凸塊來說���,更有可能因連接到相鄰焊點的一點焊料而發(fā)生短路���。但對于混合鍵合來說�,危險是導(dǎo)致連接斷開的缺陷��。

其次是背面電源技術(shù)���。在當(dāng)今的處理器中�����,所有互連(無論是承載電力還是數(shù)據(jù))都構(gòu)建在芯片的“正面”硅基板上方。而Foveros和其他3D芯片堆疊技術(shù)需要硅通孔等互連���,這些互連可以向下鉆穿硅以從另一側(cè)建立連接��。背面電力傳輸則更進(jìn)一步�,它將所有電源互連放置在硅下方�����,基本上將包含晶體管的層夾在兩組互連之間���。

這種布置會產(chǎn)生影響���,因為電源互連和數(shù)據(jù)互連需要不同的功能����。電源互連需要較寬以減少電阻���,而數(shù)據(jù)互連應(yīng)較窄以便可以密集封裝��。英特爾將成為第一家在商用芯片中引入背面供電的芯片制造商��。背面供電網(wǎng)絡(luò)技術(shù)將與英特爾芯片中的技術(shù)基本相同��,然而它在Clearwater Forest中得到了更大的利用����。即將推出的CPU在基礎(chǔ)芯片中包含所謂的“片上電壓調(diào)節(jié)器”��,使電壓調(diào)節(jié)接近其驅(qū)動的邏輯��,這意味著邏輯可以運(yùn)行得更快����。距離越短,調(diào)節(jié)器就能更快地響應(yīng)電流需求的變化��,同時消耗更少的功率。由于邏輯芯片使用背面供電�,因此電壓調(diào)節(jié)器和芯片邏輯之間的連接電阻要低得多。

除了背面電源之外���,該芯片制造商還采用英特爾20A工藝改用不同的晶體管架構(gòu):RibbonFET�����。RibbonFET是一種納米片或環(huán)柵晶體管���,自2011年以來取代了FinFET(CMOS的主力晶體管)。在Intel 18A中�,Clearwater Forest的邏輯芯片將采用第二代RibbonFET工藝制造���。Fetzer表示����,雖然這些器件本身與Intel 20A中出現(xiàn)的設(shè)備沒有太大區(qū)別�,但其設(shè)計具有更大的靈活性。

其中一些變化源于FinFET時代失去的一定程度的靈活性�。在FinFET出現(xiàn)之前,晶體管可以制成多種寬度���,從而允許在性能(伴隨更高電流)和效率(需要更好地控制漏電流)之間進(jìn)行或多或少的連續(xù)權(quán)衡����。但由于FinFET的主要部分是具有規(guī)定高度和寬度的垂直硅鰭,因此必須通過鰭的數(shù)量進(jìn)行權(quán)衡����。例如,使用兩個翅片可以使電流加倍�����,但沒有辦法將其增加25%或50%��。而有了納米片器件����,改變晶體管寬度的能力又回來了?!癛ibbonFET技術(shù)可以在同一技術(shù)基礎(chǔ)上實現(xiàn)不同尺寸的焊帶?���!盕etzer說道?���!爱?dāng)我們從英特爾20A轉(zhuǎn)向英特爾18A時�,我們在晶體管尺寸方面提供了更大的靈活性���?!?/p>

這種靈活性意味著設(shè)計人員可以用來構(gòu)建系統(tǒng)的標(biāo)準(zhǔn)單元(基本邏輯塊)可以包含具有不同屬性的晶體管�����。這使得英特爾能夠開發(fā)出一個“增強(qiáng)型庫”��,其中包括比英特爾20A工藝的標(biāo)準(zhǔn)單元更小�����、性能更好或更高效的標(biāo)準(zhǔn)單元��。

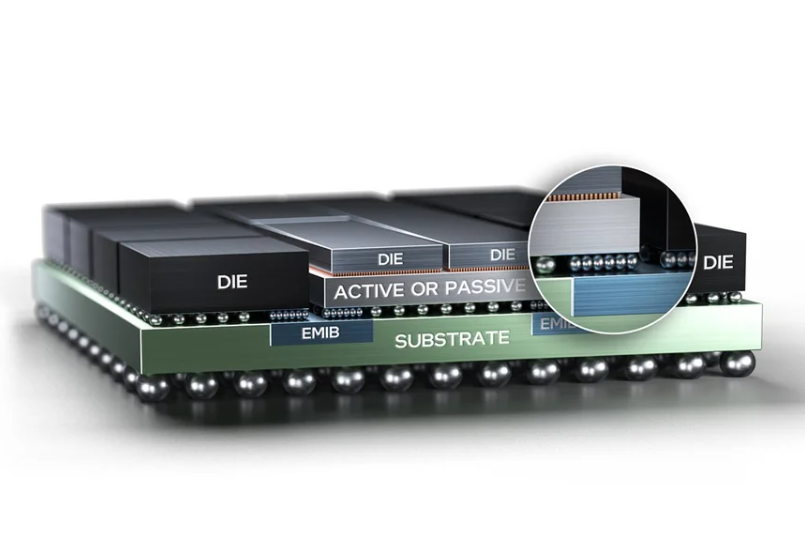

最后是第二代EMIB技術(shù)�。在Clearwater Forest中��,處理輸入和輸出的芯片使用第二代英特爾EMIB水平連接到基礎(chǔ)芯片�����。EMIB是一小塊硅,包含一組密集的互連和微凸塊��,旨在將同一平面中的一個芯片連接到另一個芯片����。硅嵌入封裝本身以形成芯片之間的橋梁。自Sapphire Rapids于2023年發(fā)布以來���,該技術(shù)已在英特爾CPU中投入商業(yè)使用��。它是一種成本較低的替代方案����,可將所有芯片放在硅中介層上��,硅中介層是一塊帶有互連圖案的硅片����,大小足以容納所有待放置的系統(tǒng)芯片。除了材料成本之外�,硅中介層的制造成本可能很高,因為它們通常比標(biāo)準(zhǔn)硅工藝設(shè)計的尺寸大幾倍���。

第二代EMIB技術(shù)今年與Granite Rapids CPU一起首次亮相����,它將微凸塊連接的間距從55微米縮小到45微米并提高了電線的密度。此外�,就Clearwater Forest而言,“還存在一些獨(dú)特的挑戰(zhàn)�����,因為我們將常規(guī)芯片上的EMIB連接到Foveros Direct 3D基礎(chǔ)芯片和堆棧上的EMIB��?��!盕etzer說道����。他說這種情況最近被重新命名為EMIB 3.5技術(shù)(以前稱為co-EMIB)�,需要采取特殊步驟來確保所涉及的應(yīng)力和應(yīng)變,與Foveros堆棧中的硅兼容����,而Foveros堆棧通常比普通芯片更薄���。

以上是英特爾在圣何塞活動上分享的未來數(shù)據(jù)中心處理器技術(shù)及其為代工客戶提供的新芯片技術(shù)的詳細(xì)內(nèi)容��。這些技術(shù)包括更密集的邏輯�、3D堆疊芯片內(nèi)連接性增加16倍、背面電源�����、RibbonFET晶體管架構(gòu)以及第二代EMIB技術(shù)等����,它們共同構(gòu)成了英特爾未來數(shù)據(jù)中心處理器的核心競爭力,并有望為整個行業(yè)帶來重大的變革和進(jìn)步�����。

發(fā)布者:溫暖陽光最新更新時間:2024-02-22?來源: IEEE關(guān)鍵字:英特爾?

如有內(nèi)容侵權(quán)或違規(guī)�,請聯(lián)系處理,郵箱地址:betty@pioneeric.com